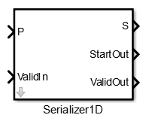

Serializer1D

Convert vector signal to scalar or smaller vectors

Library

HDL Coder / HDL Operations

Description

The Serializer1D block converts a slower vector signal into a faster stream of scalar signals or smaller size vector signals based on the Ratio and Idle Cycle values. To match the faster serialized output, the sample time changes according to this equation:

Consider this example where the input data is a vector of size 4 and the Ratio is set to 4.

The output data serializes each of the vector signals into four scalar signals. The sample time at the output is: .

To add idle cycles at the end of each output, for Idle Cycles, specify an integer greater than zero. Consider this example with Ratio set to 4 and Idle Cycles set to 2.

For each slow vector signal, the output has six fast cycles consisting of the four serialized scalar signals and two idle cycles. The sample time at the output is .

The Serializer1D block provides three control signals: ValidIn, ValidOut, and StartOut. You can use ValidIn to control ValidOut and StartOut. The serialized output does not depend on ValidIn. To determine whether the output serialized data is valid, use ValidIn and ValidOut. If you give a high input to ValidIn, and there are no idle cycles, ValidOut gives a high output, which indicates that the output serialized data is valid.

Consider an example that has input data as a vector of size 4, Ratio set to 4, Idle Cycles set to 2, and uses all three control signals.

For the first input vector, ABCD, ValidIn is

false. StartOut and ValidOut become false.

This means that the output data values are not valid. In the waveform, the data values

are represented as X, which correspond to don’t

care values.

For the second input vector, ABCE, ValidIn is

true. The output data serializes the vector into four scalar signals. The control signal

StartOut becomes true at output A to

indicate the start of deserialization. In the next cycle, the

StartOut signal becomes false. ValidOut is

true for all four output signals indicating valid output

data for the four cycles. ValidOut becomes false for the idle

cycles, and the output data values are don’t care values.

Parameters

- Ratio

Serialization factor, specified as a positive scalar. Default is

1.The ratio is equal to the size of the input vector divided by the size of the output vector. Input vector size must be divisible by the ratio.

- Idle Cycles

Number of idle cycles to add at the end of each output. Default is

0.- ValidIn

Activates the ValidIn port. Default is

off.- StartOut

Activates the StartOut port. Default is

off.- ValidOut

Activates the ValidOut port. Default is

off.

- Input data port dimensions (-1 for inherited)

Size of the input data signal. Input vector size must be divisible by the ratio. By default, the block inherits size based on the context within the model.

- Input sample time (-1 for inherited)

Time interval between sample time hits, or another appropriate sample time such as continuous. By default, the block inherits sample time based on context within the model. For more information, see Sample Time.

- Input signal type

Input signal type of the block, specified as

auto,real, orcomplex. Default isauto.

Ports

PInput signal to serialize. Bus data types are not supported.

ValidInInput control signal. This port is available when you select the ValidIn check box.

Data type: Boolean

SSerialized output signal. Bus data types are not supported.

StartOutOutput control signal that indicates where to start deserialization. You can use this signal as the StartIn input to the Deserializer1D block. To use this port, select the StartOut check box.

Data type: Boolean

ValidOutOutput control signal that indicates valid output signal. You can use this signal as the ValidIn input to the Deserializer1D block. This port is available when you select the ValidOut check box.

Data type: Boolean