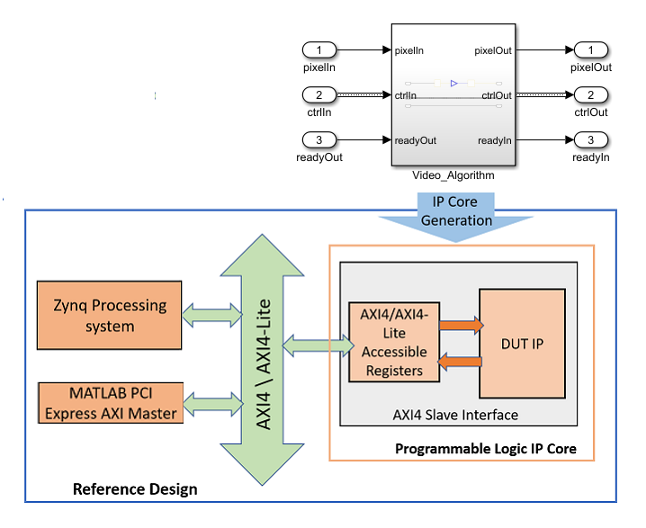

Define Multiple AXI Master Interfaces in Reference Designs to access DUT AXI4 Slave Interface

You can define multiple AXI Master interfaces in your custom reference design and access the AXI4 slave interfaces in the generated HDL DUT IP core for the DUT. This capability enables you to simultaneously connect the HDL DUT IP core to two or more AXI Master IP in the reference design, such as the HDL Verifier™ JTAG AXI Master IP and the ARM® processor in the Zynq® processing system.

Vivado-Based Reference Designs

To define multiple AXI Master interfaces, you specify the

BaseAddressSpace and MasterAddressSpace

for each AXI Master instance, and also the IDWidth

property.

IDWidth is the width of all ID

signals, such as AWID, WID,

ARID, and RID, specified as a positive

integer. By default, the IDWidth is 12,

which enables you to specify one AXI Master interface connection to the DUT IP core.

To connect the DUT IP core to multiple AXI Master interfaces, you may have to

increase the IDWidth. The IDWidth value is

tool-specific. To see the value that you must use when specifying more than one AXI

Master interface, refer to the documentation for that tool. If you use an incorrect

ID width, the synthesis tool generates an error, and reports the correct

IDWidth that you must use.

This code is the syntax for the MasterAddressSpace field when

specifying multiple AXI Master interfaces in Vivado®-based reference

designs:

'MasterAddressSpace', ...

{'AXI Master Instance Name1/Address Space of Instance Name1', ...

'AXI Master Instance Name2/Address_Space of Instance Name2',...};For example, this code illustrates how you can modify the

plugin_rd file to define two AXI Master interfaces.

% ... %% Add custom design files % add custom Vivado design hRD.addCustomVivadoDesign( ... 'CustomBlockDesignTcl', 'system_top.tcl', ... 'VivadoBoardPart', 'xilinx.com:zc706:part0:1.0'); % ... % ... % The DUT IP core in this reference design is connected % to both Zynq Processing System and the MATLAB as AXI % Master IP. Because of 2 AXI Master, ID width % has to be increased from 12 to 13. hRD.addAXI4SlaveInterface( ... 'InterfaceConnection', 'axi_interconnect_0/M00_AXI', ... 'BaseAddress', {'0x40010000', '0x40010000'}, ... 'MasterAddressSpace', {'processing_system7_0/Data', 'hdlverifier_axi_master_0/axi4m'}, ... 'IDWidth', 13); % ...

In this example, the two AXI Master IP are the HDL Verifier MATLAB as AXI Master IP and the ARM processor. Based on the syntax of

the MasterAddressSpace, for the HDL Verifier MATLAB as AXI Master IP, the AXI Master Instance

Name is hdlverifier_axi_master_0 and the

Address_Space of Instance Name is

axi4m.

The AXI4 slave interfaces in the HDL DUT IP core connect to the Xilinx® AXI Interconnect IP that is defined by the

InterfaceConnection property of the

addAXI4SlaveInterface method. The AXI4 slave interfaces have a

BaseAddress. This BaseAddress must map to

the MasterAddressSpace for the two AXI Master IP, which is

specified as a cell array of character vectors.

You must make sure that the AXI Master IPs have already been included in the

Vivado reference design project. system_top.tcl is the TCL

file that is defined by the CustomBlockDesignTcl property of

the addCustomVivadoDesign method. In

this TCL file, you must make sure that the two AXI Master IP are connected to the

same Xilinx AXI Interconnect IP. The interconnects then connect the AXI Master IPs

to the AXI4 slave interfaces in the HDL IP core.

After you run the IP Core Generation workflow and create the

Vivado project, open the project. In the Vivado project, if you open the block design, you see the two AXI Master IP

connected to the HDL DUT IP core. If you select the Address

Editor tab, you see the AXI Master instance names and the

corresponding address spaces.

Qsys-Based Reference Designs

To define multiple AXI Master interfaces, you specify the

InterfaceConnection and BaseAddressSpace

for each AXI Master instance, and also the IDWidth property. This

code is the syntax for the InterfaceConnection field when

specifying multiple AXI Master interfaces in Qsys™-based

reference

designs:

'InterfaceConnection', ...

{'AXI Master Instance Name1/Port name of Instance Name1', ...

'AXI Master Instance Name2/Port name of Instance Name1', ...};For example, this code illustrates how you can modify the

plugin_rd file to define three AXI Master

interfaces.

% ... %% Add custom design files % add custom Qsys design hRD.addCustomQsysDesign('CustomQsysPrjFile', 'system_soc.qsys'); hRD.CustomConstraints = {'system_soc.sdc','system_setup.tcl'}; % ... % add AXI4 slave interfaces hRD.addAXI4SlaveInterface( ... 'InterfaceConnection', {'hps_0.h2f_axi_master','master_0.master','MATLAB_as_AXI_Master_0.axm_m0'}, ... 'BaseAddress', {'0x0000_0000','0x0000_0000','0x0000_0000'},... 'InterfaceType', 'AXI4'... 'IDWidth', 14); % ...

Based on the syntax of the InterfaceConnection option, for the

HDL Verifier MATLAB as AXI Master IP, the AXI Master Instance

Name is MATLAB_as_AXI_Master_0 and the

Port name is axm_m0. For each AXI Master

IP, the BaseAddress of the HDL IP core and

InterfaceConnection must be specified as a cell array of

character vectors.

You must make sure that the AXI Master IPs have already been included in the Qsys

reference design project. system_soc.qsys is the file that is

defined by the CustomQsysPrjFile property of the addCustomQsysDesign method. In this

file, you must make sure that the two AXI Master IP are connected to the same Qsys

AXI Interconnect IP.

The interconnects then connect the AXI Master IPs to the AXI4 slave interfaces in the HDL IP core.

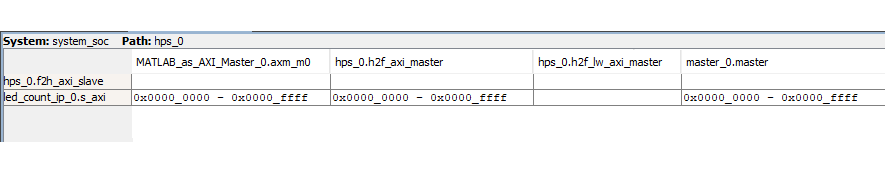

After you run the IP Core Generation workflow and create the

Quartus® project, open the project. In the Quartus project, you see the three AXI Master IP and the AXI Master interfaces

connected to the HDL IP core for the DUT. If you select the Address

Map tab, you see the AXI Master instance names, the port names, and

the corresponding address spaces.

See Also

hdlcoder.Board | hdlcoder.ReferenceDesign

Related Examples

- Define Custom Board and Reference Design for Zynq Workflow

- Define Custom Board and Reference Design for Intel SoC Workflow