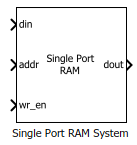

Single Port RAM System

Single Port RAM block based on hdl.RAM system object with ability to provide initial value

- Library:

HDL Coder / HDL RAMs

Description

The blocks are MATLAB System blocks that use the

hdl.RAM

System object™. You can specify the RAM type as Dual port,

Simple dual port, or Single port. In terms of

simulation behavior, the Single Port RAM System block behaves similar to

the Single Port RAM.

By using the MATLAB System block implementation, you can:

Specify an initial value for the RAM. In the Block Parameters dialog box, enter a value for Specify the RAM initial value.

Obtain faster simulation results when you use these blocks in your Simulink® model.

Create parallel RAM banks when you use vector data by leveraging the

hdl.RAMSystem object functionality.Obtain higher performance and support for large data memories.

Limitations

The block does not support

booleaninputs. Cast anybooleantypes toufix1for input to the block.When you build the FPGA bitstream for the RAM, the global reset logic does not reset the RAM contents. To reset the RAM, make sure that you implement the reset logic.

The RAM address can be either

fixed-point (fi)orinteger, must be unsigned, and must be between2and31bits long.