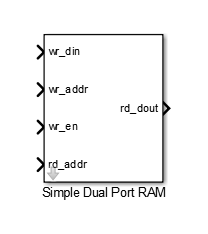

Simple Dual Port RAM

Dual port RAM with single output port

Library

HDL Coder / HDL RAMs

Description

The Simple Dual Port RAM block models RAM that supports simultaneous read and write operations, and has a single output port for read data. You can use this block to generate HDL code that maps to RAM in most FPGAs.

The Simple Dual Port RAM is similar to the Dual Port RAM, but the Dual Port RAM has both a write data output port and a read data output port.

Read-During-Write Behavior

During a write operation, if a read operation occurs at the same address, old data appears at the output.

Parameters

- Address port width

Address bit width. Minimum bit width is 2, and maximum bit width is 29. The default is 8.

Ports

The block has the following ports:

wr_dinWrite data input. The data can have any width. It inherits the width and data type from the input signal.

Data type: scalar fixed point, integer, or complex

wr_addrWrite address.

Data type: scalar unsigned integer (

uintN) or unsigned fixed point (ufixN) with a fraction length of0wr_enWrite enable.

Data type: Boolean

rd_addrRead address.

Data type: scalar unsigned integer (

uintN) or unsigned fixed point (ufixN) with a fraction length of0rd_doutOutput data from read address,

rd_addr.