IP Core Generation Workflow for Speedgoat Simulink-Programmable I/O Modules

HDL Coder™ uses the IP Core Generation workflow

infrastructure to generate a reusable HDL IP core for the Speedgoat

Simulink-Programmable I/O modules that support Xilinx®

Vivado®. The workflow produces an IP core report that displays the target

interface configuration and the code generator settings that you specify. You can

integrate the IP core into a larger design by adding it in an embedded system

integration environment. See Custom IP Core Generation.

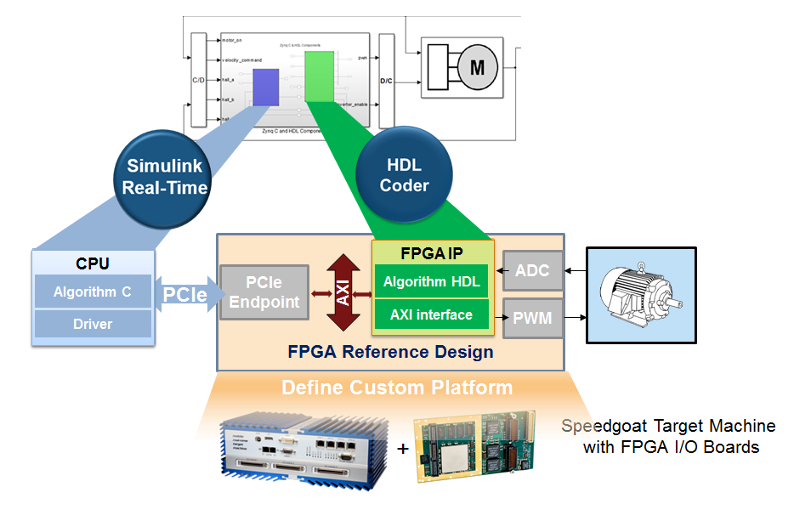

This figure shows how the software generates an IP core with an AXI interface and integrates the IP core into the FPGA reference design.

Supported I/O Modules

To learn about I/O modules that HDL Coder supports with the Simulink Real-Time FPGA

I/O workflow, see Speedgoat FPGA Support with HDL Workflow Advisor.

IP Core Generation Workflow

This workflow has these key features:

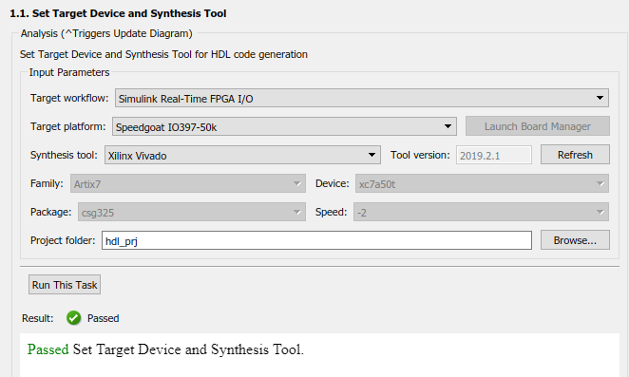

Uses Xilinx Vivado as the synthesis tool.

Generates a reusable and sharable IP core. The IP core packages the RTL code, a C header file, and the IP core definition files.

Creates a project for integrating the IP core into the Speedgoat reference design.

Generates an FPGA bitstream and downloads the bitstream to the target hardware.

After building the FPGA bitstream, the workflow generates a Simulink® Real-Time™ model. The model is an interface subsystem model that contains the blocks to program the FPGA and communicate with the I/O module through the PCIe bus during real-time execution.

Restrictions

IP Core Generation workflow does not support :

RAM Architecture set to

Generic RAM without clock enable.Using different clocks for the IP core and the AXI interface. The

IPCore_ClkandAXILite_ACLKmust be synchronous and connected to the same clock source. TheIPCore_RESETNandAXILite_ARESETNmust be connected to the same reset source. See Synchronization of Global Reset Signal to IP Core Clock Domain.

Related Topics

- Speedgoat FPGA Support with HDL Workflow Advisor

- FPGA Programming and Configuration on Speedgoat Simulink-Programmable I/O Modules

- Custom IP Core Generation