FPGA Floating-Point Library Targeting Parameters

This section contains parameters in the HDL Code Generation > Floating Point pane of the Configuration Parameters dialog box. Use these parameters to specify the latency strategy, objective, and whether to initialize the pipeline registers in the floating-point target IP to zero.

Initialize IP Pipelines To Zero

Inserts additional logic during HDL code generation to initialize the values of pipeline registers in the Altera® floating-point target IP to zero. If you do not select this check box, HDL Coder™ reports a warning during HDL code generation.

Settings

Default: On

On

On Inserts additional logic to initialize pipeline registers in the floating-point target IP to zero.

Off

OffDoes not add additional logic to initialize pipeline registers in the floating-point target IP to zero.

Dependency

To specify this parameter, set the Floating Point IP Library to

Altera Megafunctions (ALTERA FP FUNCTIONS). Before you set

the floating-point library, specify the path to your synthesis tool by using the

hdlsetuptoolpath function.

Command-Line Information

To specify this setting:

Create a floating-point target configuration object with

Altera Megafunctions (ALTERA FP FUNCTIONS)as the floating-point target library.fpconfig = hdlcoder.createFloatingPointTargetConfig('AlteraFPFunctions');Specify the

InitializeIPPipelinesToZeroproperty of theLibrarySettingsattribute of the floating-point target configuration object.fpconfig.LibrarySettings.InitializeIPPipelinesToZero = 0;

Set the floating-point target configuration on the model and then generate HDL code. This example shows how to set the configuration on the

sfir_singlemodel and generate HDL code for thesymmetric_firsubsystem:hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig) makehdl('sfir_single/symmetric_fir')

See Also

Latency Strategy

Specify whether you want the design to map to minimum or maximum latency with Xilinx® LogiCORE or ALTFP Altera megafunction IPs.

Settings

Default:

MIN

The options are:

MINMaps to minimum latency for the specified floating-point target IP.

MAXMaps to maximum latency for the specified floating-point target IP.

Dependency

To specify this parameter, set the Floating Point IP Library to

Altera Megafunctions (ALTFP) or Xilinx

LogiCORE. Before you set the floating-point library, specify the path to

your synthesis tool by using the hdlsetuptoolpath function.

Command-Line Information

To specify this setting:

Create a floating-point target configuration object with

Altera Megafunctions (ALTERA FP FUNCTIONS)as the floating-point target library.fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTFP');Specify the

LatencyStrategyproperty of theLibrarySettingsattribute of the floating-point target configuration object.fpconfig.LibrarySettings.LatencyStrategy = 'MAX';

Set the floating-point target configuration on the model and then generate HDL code. This example shows how to set the configuration on the

sfir_singlemodel and generate HDL code for thesymmetric_firsubsystem:hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig) makehdl('sfir_single/symmetric_fir')

See also

Objective

Specify whether you want to optimize the design for speed or area when mapping to floating-point target libraries.

Settings

Default:

SPEED

The options are:

NONESelect this option if you do not want to optimize the design for speed or area.

SPEEDSelect this option to optimize the design for speed.

AREASelect this option to optimize the design for area.

Dependency

To specify this parameter, set the Floating Point IP Library to

Altera Megafunctions (ALTFP) or Xilinx

LogiCORE. Before you set the floating-point library, specify the path to

your synthesis tool by using the hdlsetuptoolpath function.

Command-Line Information

To specify this setting:

Create a floating-point target configuration object with

Altera Megafunctions (ALTERA FP FUNCTIONS)as the floating-point target library.fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTFP');Specify the

Objectiveproperty of theLibrarySettingsattribute of the floating-point target configuration object.fpconfig.LibrarySettings.Objective = 'AREA';

Set the floating-point target configuration on the model and then generate HDL code. This example shows how to set the configuration on the

sfir_singlemodel and generate HDL code for thesymmetric_firsubsystem:hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig) makehdl('sfir_single/symmetric_fir')

See also

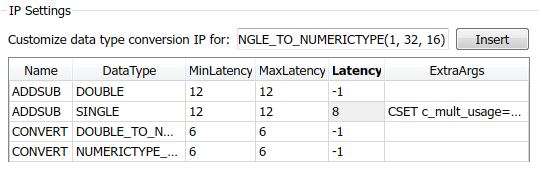

IP Settings

The IP Settings section has an IP configuration table with the IP names and data types and additional options to specify a custom latency and any extra arguments.

The options in the IP configuration table depend on the library that you specify.

If you specify the

ALTERA MEGAFUNCTION (ALTERA FP FUNCTIONS)library, HDL Coder infers the latency value from the Target Frequency (MHz) value.If you specify the

ALTERA MEGAFUNCTION (ALTFP)orXILINX LOGICORElibraries, HDL Coder infers the IP latency from the Latency Strategy setting. The IP configuration table has two additional columns, MinLatency and MaxLatency, that contain the minimum and maximum latency values for each IP in the table.

The IP configuration table has these sections:

Name: Contains a list of IP names that HDL Coder map the Simulink® blocks to, such as

ABS,ADDSUB, andCONVERT.DataType: Contains a list of IP data types for each IP in the table. These are mostly

SINGLEandDOUBLEdata types. TheCONVERTIP blocks can haveDOUBLE_TO_NUMERICTYPE,NUMERICTYPE_TO_DOUBLEdata types, and so on.Latency: The default latency value of

–1means that the IP inherits the latency value from the target frequency or the latency strategy setting depending on the library that you choose. To customize the latency of the IP that your Simulink blocks map to, enter your own custom value for the latency.ExtraArgs: Specify any additional settings that is specific to the IP.

For example, if you have an Add block with

Single data types in your Simulink model, HDL Coder maps the block to the ADDSUB IP. If you

want to specify a custom latency value, say 8, for the IP, enter the value in the

Latency column for the IP.

cmultusage is a parameter that you can specify with the Xilinx

LogiCORE® libraries.

Dependency

To specify this parameter, set the Floating Point IP Library to

Altera Megafunctions (ALTFP) or Xilinx

LogiCORE. Before you set the floating-point library, specify the path to

your synthesis tool by using the hdlsetuptoolpath function.

Command-Line Information

To specify this setting:

Create a floating-point target configuration object with

Altera Megafunctions (ALTERA FP FUNCTIONS)as the floating-point target library.fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTFP');To view the floating-point IP configuration, use the

IPConfigobject.fpconfig.IPConfig

To customize the latency or specify additional arguments, use the

customizemethod.fpconfig.IPConfig.customize('ADDSUB','Single','Latency',6);Set the floating-point target configuration on the model and then generate HDL code. This example shows how to set the configuration on the

sfir_singlemodel and generate HDL code for thesymmetric_firsubsystem:hdlset_param('sfir_single','FloatingPointTargetConfig',fpconfig) makehdl('sfir_single/symmetric_fir')