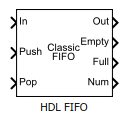

HDL FIFO

Stores sequence of input samples in first in, first out (FIFO) register

- Library:

HDL Coder / HDL RAMs

Description

The HDL FIFO block stores a sequence of input samples in a first in, first out (FIFO) register. The data written first into the FIFO register comes out first. The block implementation resembles the FIFO unit in hardware platforms in terms of functionality and behavior.

Ports

Input

In — Data input signal

scalar

Data input signal to the FIFO block. When you write data into the FIFO, the newest data is pushed to the end of the FIFO register. The block pushes subsequent data entries below this entry.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Push — Write control signal

scalar

When this port receives a value of 1, the block

pushes the input at the In port onto the end of the

FIFO register.

Data Types: Boolean

Pop — Read control signal

scalar

When this port receives a value of 1, the block

pops the first element off the FIFO register and holds the

Out port at that value.

Data Types: Boolean

Note

If two or more of the control input ports are triggered in the same time step, the pop operation executes first, followed by the push operation.

Output

Out — Data output signal

scalar

Data output signal from the FIFO block. When you read data from the FIFO, the data that you wrote first into the FIFO register comes off the FIFO and is held at the output.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Empty — Data output signal

scalar

Control signal output from the FIFO that becomes 1

when the FIFO register is empty and does not contain data

entries.

Dependencies

To enable this port, Show empty register indicator port (Empty) must be selected.

Data Types: Boolean

Full — Data output signal

scalar

Control signal output from the FIFO that becomes 1

when the FIFO register is full and cannot take more data entries.

Dependencies

To enable this port, Show full register indicator port (Full) must be selected.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Num — Number of entries

scalar

Number of data entries that are currently inside the FIFO register.

Num increments by 1 for

every data that you write into the FIFO. Num

decrements by 1 for every data that you read from the

FIFO.

Dependencies

To enable this port, Show number of entries register port (Num) must be selected.

Data Types: single | double | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | Boolean | fixed point

Parameters

Register size — Number of entries

10 (default)

Specify the number of entries that the FIFO register can hold. The default

value for Register size is 10. The

minimum value for Register size is

4.

Programmatic Use

Block parameter:

fifo_size |

| Type: character vector |

| Value: An integer greater than or equal to four |

Default:

'10' |

Mode — Operation mode

'Classic' (default) | 'FWFT'

Specify the operation mode of the FIFO. By default, the

Mode is set to Classic. You see

that the block icon displays Classic FIFO. You can change

the Mode to FWFT. When you change

the Mode, the block icon displays FWFT

FIFO. By using the FWFT mode, you can

lookahead and see the first word written to the FIFO register without

placing a read request. The FWFT mode is especially useful when you apply

the back-pressure with AXI4-Stream interfaces.

Programmatic Use

Block parameter:

mode |

| Type: character vector |

Value:

'Classic' | 'FWFT' | |

Default:

'Classic' |

The ratio of output sample time to input sample time — Sample rate ratio

1 (default)

Specify the ratio of output sample time to input sample time. The default

ratio is 1, which means that the inputs

In and Push, and outputs

Out and Pop, run at the same

sample rate. The inputs and outputs can run at different sample times. Use a

positive integer or 1/N, where N is a

positive integer. For example, if you enter 1/2, the

output sample time is half the input sample time, or the outputs run faster.

The Full, Empty, and

Num signals run at the faster rate.

Programmatic Use

Block parameter:

ratio |

| Type: character vector |

| Value: An integer greater than or equal to one |

Default:

'1' |

Push onto full register — Overflow condition

'Warning' (default) | 'Ignore' | 'Error'

Specify how you want the block to respond when you write to a FIFO that is

full. The default is Warning.

Programmatic Use

Block parameter:

push_msg |

| Type: character vector |

Value:

'Warning' | 'Ignore' |

'Error' |

Default:

'Warning' |

Pop onto empty register — Underflow condition

'Warning' (default) | 'Ignore' | 'Error'

Specify how you want the block to respond when you read from a FIFO that

is empty. The default is Warning.

Programmatic Use

Block parameter:

pop_msg |

| Type: character vector |

Value:

'Warning' | 'Ignore' |

'Error' |

Default:

'Warning' |

Show empty register indicator port (Empty) — Optional empty port

on (default) | off

Specify whether to enable the Empty output port. This

port outputs a 1 when the FIFO register is empty and

0 when the FIFO contains one or more data

entries.

Programmatic Use

Block parameter:

show_empty |

| Type: character vector |

Value:

'on' | 'off' |

Default:

'on' |

Show full register indicator port (Full) — Optional full port

on (default) | off

Specify whether to enable the Full output port. This

port outputs a 1 when the FIFO register is full.

Programmatic Use

Block parameter:

show_full |

| Type: character vector |

Value:

'on' | 'off' |

Default:

'on' |

Show num register indicator port (Num) — Optional num port

on (default) | off

Specify whether to enable the Num output port. This

port outputs the number of data entries that are currently available in the

FIFO queue.

Programmatic Use

Block parameter:

show_num |

| Type: character vector |

Value:

'on' | 'off' |

Default:

'on' |

Algorithms

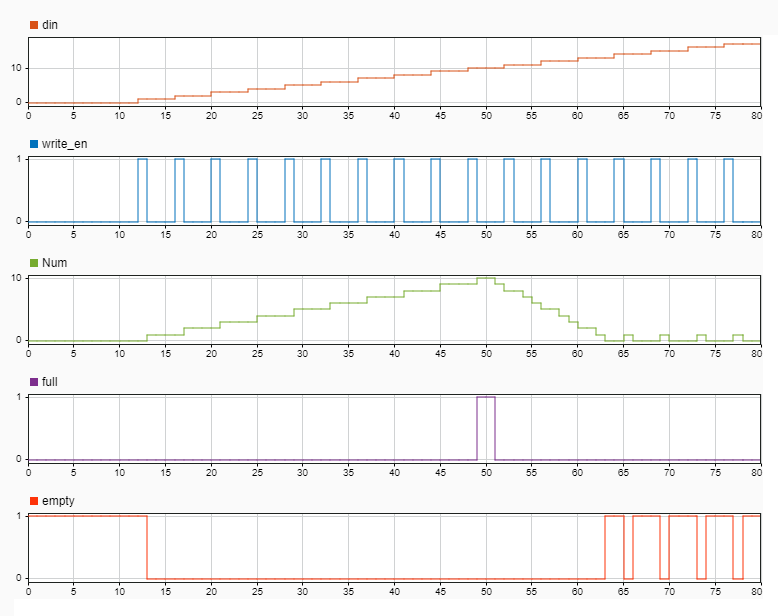

FIFO Write Operation

This figure displays the FIFO write operation. The Push input port acts as the enable signal for the write operation. This signal is denoted by the write_en signal in the figure.

When the write_en signal is 0, the block

does not write data to the FIFO and the empty flag is

asserted.

When the write_en becomes 1, the block

pushes the din signal at input port In to

the end of the FIFO register in the next time step. The Num

signal indicates the number of data entries in the FIFO register. Every time you

write data into the FIFO, the Num signal increments by

1. At time step 12,

write_en is 1. At the next time step

13, data is written to the FIFO. Num

signal increments by 1 and the empty flag is

de-asserted.

This FIFO uses the default register size of 10. When the

Num signal becomes equal to the Register

size at time step 49, the

Full signal is asserted. After the

Full signal becomes 1, if you try to

write more entries into the FIFO, the block generates a warning.

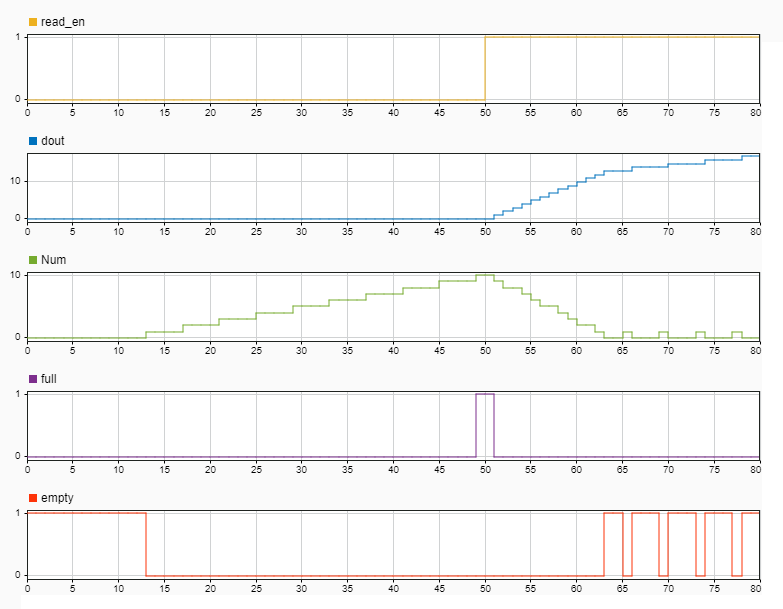

Classic FIFO Read Operation

This figure displays the FIFO read operation. The Pop input port acts as the enable signal for the read operation. This signal is denoted by the read_en signal in the figure.

When the read_en signal is 0, the block

output dout is 0. When the

read_en signal becomes 1 at time step

50, the dout signal outputs the oldest

entry in the FIFO in the next time step 51. The

Full flag is de-asserted and the Num

signal decrements by 1 starting from time step

51 as you read data from the FIFO.

When the Num signal becomes equal to 0,

the Empty signal is asserted. After the

Empty signal becomes 0, if you try to

read more entries from the FIFO, the block generates a warning.

FWFT FIFO Read Operation

This figure displays the FIFO read operation. The Pop input port acts as the enable signal for the read operation. This signal is denoted by the read_en signal in the figure.

By default, the HDL FIFO works in the Classic

mode. You can also use a first-word-fall-through (FWFT) mode for the FIFO. In the

Block Parameters dialog box, specify the Mode as

FWFT.

In the FWFT mode, the write operation works in the same way as

the Classic mode. The FWFT mode differs from

the Classic mode when you perform a read operation. In the

Classic mode, after you place a read request or input a

1 to the Pop port, the data becomes

available at the FIFO output in the next clock cycle. In the FWFT

mode, the first word you write to the FIFO falls through to the output and is

available at the output signal Out.

In the figure, though read-en becomes 1 at

time step 50, the FIFO read the first word

dout at time step 15. You can use this

capability to look ahead and see the first word that has been written to the

FIFO.

Extended Capabilities

HDL Code Generation

Generate Verilog and VHDL code for FPGA and ASIC designs using HDL Coder™.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

HDL Architecture

This block has a single, default HDL architecture.

HDL Block Properties

| General | |

|---|---|

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|