Customize Floating-Point IP Configuration

When mapping your Simulink® model to floating-point target libraries, you can create a floating-point target configuration with your own custom IP settings. To customize the IP settings, you can use an IP configuration table to choose from different combinations of IP names and data types. The table contains a list of IP types and additional columns that you can use to specify your own custom latency value and other IP settings.

The IP configuration depends on the library settings. The library settings are specific to the floating-point library that you choose. You can customize the IP latency by using the target frequency or the latency strategy setting.

Customize the IP Latency with Target Frequency

To specify the target frequency that you want the IP to achieve,

use the Altera Megafunctions (ALTERA FP Functions) library. HDL Coder™ infers

the latency of the IP based on the target frequency value. If you

do not specify the target frequency, HDL Coder sets the target

frequency to a default value of 200 MHz.

You can customize the IP latency by using the Target

Frequency setting in the Configuration Parameters dialog

box or the TargetFrequency property from the

command line.

From the UI

To customize the IP latency by using the target frequency setting:

Specify the library:

In the Apps tab, select HDL Coder. The HDL Code tab appears. Click Settings.

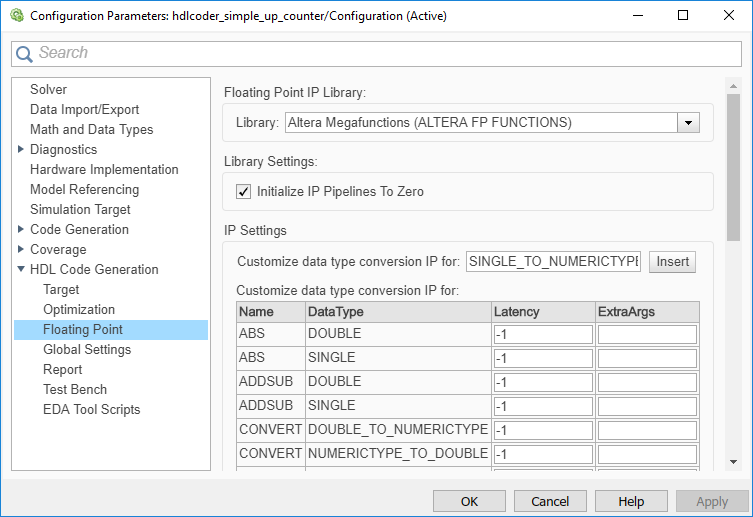

On the HDL Code Generation > Floating Point Target pane, for Library, select

Altera Megafunctions (ALTERA FP Functions).

Specify the target frequency: In the Target pane, for Target Frequency (MHz), enter the target frequency that you want the floating-point IP to achieve. If you do not specify a target frequency, HDL Coder sets the target frequency to a default value of

200 MHz.Specify the library settings: By using the Initialize IP Pipelines to Zero option, you can specify whether to initialize pipeline registers in the IP to zero. To avoid potential numerical mismatches in the HDL simulation, it is recommended to leave the Initialize IP Pipelines to Zero option set to

true.Specify the IP settings: In the IP configuration table, you can optionally specify a custom latency and any additional settings specific to the IP.

In the Latency column of the table, the default latency value of

–1means that the IP inherits the latency value from the target frequency. If you specify a latency value, HDL Coder tries to map your Simulink model to the IP at a target frequency corresponding to that latency value.In the ExtraArgs column of the table, you can specify additional settings specific to the IP.

Generate code: Click Apply. On the Simulink Toolstrip, click Generate HDL Code.

At the Command Line

To customize the IP latency from the command line:

Specify the library: Create a

hdlcoder.FloatingPointTargetConfigobject for the floating-point library by using thehdlcoder.createFloatingPointTargetConfigfunction. Then, usehdlset_paramto save the configuration on the model.For example, for an

sfir_singlemodel, to create a floating-point target configuration for theAltera Megafunctions (ALTERA FP FUNCTIONS)library with the default settings, enter:To see the default settings for the floating-point IP, enterfpconfig = hdlcoder.createFloatingPointTargetConfig('ALTERAFPFUNCTIONS'); hdlset_param('sfir_single', 'FloatingPointTargetConfiguration', fpconfig);

fpconfig.fpconfig = FloatingPointTargetConfig with properties: Library: 'ALTERAFPFUNCTIONS' LibrarySettings: [1×1 fpconfig.FrequencyDrivenMode] IPConfig: [1×1 hdlcoder.FloatingPointTargetConfig.IPConfig]Specify the target frequency: If you choose

ALTERA MEGAFUNCTION (ALTERA FP FUNCTIONS)as the library, you can create a floating-point configuration with a custom target frequency. To specify the target frequency for the IP to achieve, use theTargetFrequencyproperty. For example:hdlset_param('sfir_single', 'TargetFrequency', 300);

Specify the library settings: Specify whether you want to initialize the pipeline registers in the IP to zero. Use the

InitializeIPPipelinesToZeroproperty of thefpconfig.LibrarySettingsfunction.For example, to set the

InitializeIPPipelinesToZeroproperty to false, enter:To see the library settings that you have applied, enterfpconfig.LibrarySettings.InitializeIPPipelinesToZero = false;

fpconfig.LibrarySettings.To avoid potential numerical mismatches in the HDL simulation, it is recommended to leaveans = FrequencyDrivenMode with properties: InitializeIPPipelinesToZero: 0InitializeIPPipelinesToZeroset totrue.Specify the IP settings: With the

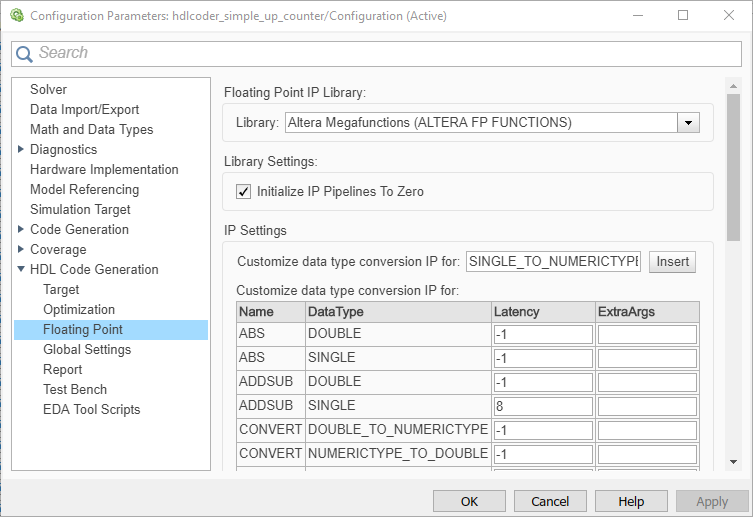

IPConfigmethod, use theLatencyandExtraArgsto customize the latency of the IP and specify any additional settings specific to the IP.For example, when mapping to the ADDSUB IP with Xilinx® LogiCORE libraries, to specify a custom latency of 8:

To see the IP settings that you have applied, enterfpconfig.IPConfig.customize('ADDSUB', 'SINGLE', 'Latency', 8);

fpconfig.IPConfig.ans = Name DataType Latency ExtraArgs _________ _______________________ _______ _________ 'ABS' 'DOUBLE' -1 '' 'ABS' 'SINGLE' -1 '' 'ADDSUB' 'DOUBLE' -1 '' 'ADDSUB' 'SINGLE' 8 '' 'CONVERT' 'DOUBLE_TO_NUMERICTYPE' -1 '' 'CONVERT' 'NUMERICTYPE_TO_DOUBLE' -1 '' 'CONVERT' 'NUMERICTYPE_TO_SINGLE' -1 '' 'CONVERT' 'SINGLE_TO_NUMERICTYPE' -1 ''Generate HDL code: To generate code from the subsystem, use

makehdl.

Customize the IP Latency with Latency Strategy

To customize the IP latency with the latency strategy setting,

use the ALTERA MEGAFUNCTION (ALTFP) or XILINX

LOGICORE libraries. Specify whether to map your Simulink model

to maximum or minimum latency. HDL Coder infers the latency of

the IP from the latency strategy setting.

You can customize the IP latency in the Configuration Parameters dialog box or from the command line.

From the UI

To customize the IP latency with the latency strategy setting:

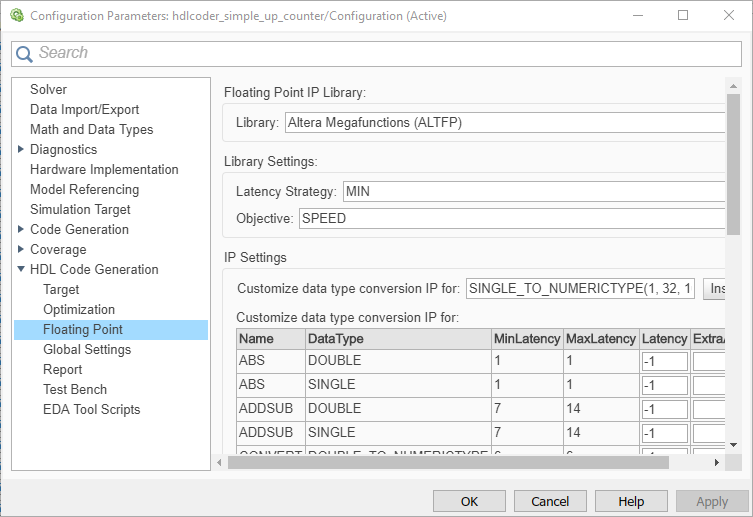

Specify the library: In the Configuration Parameters dialog box, on the HDL Code Generation > Floating Point Target pane, for Library, select

ALTERA MEGAFUNCTION (ALTFP)orXILINX LOGICORE.

Specify the library settings: For Latency Strategy, specify whether to map your Simulink model to the minimum or maximum latency for the IP. For Objective, specify whether to optimize for speed or area.

Specify the IP settings: An IP configuration table appears that contains the IP types, and their maximum and minimum latencies. In the table, you can optionally specify a custom latency and any additional settings specific to the IP.

In the Latency column of the table, the default latency value of

–1means that the IP inherits the latency value from the library settings. To customize the latency of the IP that your Simulink blocks map to, enter a value for the latency.For example, when mapping to the ADDSUB IP with Xilinx LogiCORE, if you specify a latency of 8, the latency of the IP changes to 8 instead of the default value of 12.

In the ExtraArgs column of the table, specify any additional settings specific to the IP.

For example, when mapping to Xilinx LogiCORE IP, for ExtraArgs, you can specify the parameter c_mult_usage to control the DSP resources that you want to use. To learn more about the parameter usage and syntax, see the IP library documentation.

Generate code: Click Apply. On the Simulink Toolstrip, click Generate HDL Code.

From the Command Line

To customize the IP latency from the command line:

Specify the library: Create a

hdlcoder.FloatingPointTargetConfigobject for the floating-point library by using thehdlcoder.createFloatingPointTargetConfigfunction. Then, usehdlset_paramto save the configuration on the model.For example, for an

sfir_singlemodel, to create a floating-point target configuration for theALTERA MEGAFUNCTION (ALTFP)library with the default settings, enter:By default, the library uses the minimum latency and speed objective for the floating-point IP.fpconfig = hdlcoder.createFloatingPointTargetConfig('ALTFP'); hdlset_param('sfir_single', 'FloatingPointTargetConfiguration', fpconfig);

Specify the library settings: Customize the library settings with the

ObjectiveandLatencyStrategyof thefpconfig.LibrarySettingsfunction.For example, to customize the

ALTERA MEGAFUNCTION (ALTFP)library to use the maximum latency and objective as area, enter:To see the library settings that you have applied, enterfpconfig.LibrarySettings.Objective = 'AREA'; fpconfig.LibrarySettings.LatencyStrategy = 'MAX';

fpconfig.LibrarySettings.ans = LatencyDrivenMode with properties: LatencyStrategy: 'MAX' Objective: 'AREA' fpconfig is a variable of type hdlcoder.FloatingPointTargetConfig.Specify the IP settings: With the

IPConfigmethod, use theLatencyandExtraArgsto customize the latency of the IP and specify any additional settings specific to the IP.For example, when mapping to the ADDSUB IP with Xilinx LogiCORE libraries, to use a custom latency of 8 and to specify the DSP resource usage with the

cmultusageparameter:To see the IP settings that you have applied, enterfpconfig.IPConfig.customize('ADDSUB', 'SINGLE', 'Latency', 8, 'ExtraArgs', 'CSET c_mult_usage=Full_usage');

fpconfig.IPConfig.ans = Name DataType MinLatency MaxLatency Latency ExtraArgs _________ _______________________ __________ __________ _______ ______________________________ 'ADDSUB' 'DOUBLE' 7 14 -1 '' 'ADDSUB' 'SINGLE' 7 14 8 'CSET c_mult_usage=Full_usage' 'CONVERT' 'DOUBLE_TO_NUMERICTYPE' 6 6 -1 '' 'CONVERT' 'NUMERICTYPE_TO_DOUBLE' 6 6 -1 '' 'CONVERT' 'NUMERICTYPE_TO_SINGLE' 6 6 -1 ''Generate HDL code: To generate code from the subsystem, use

makehdl.